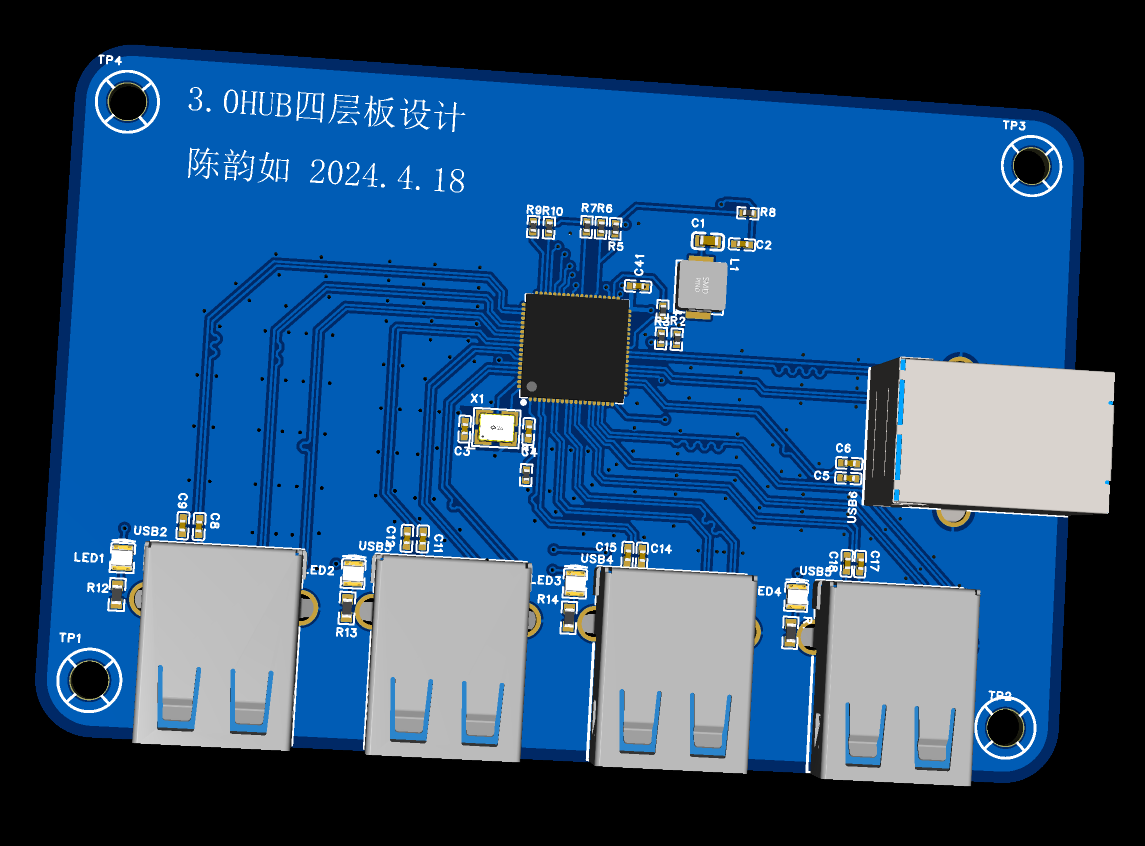

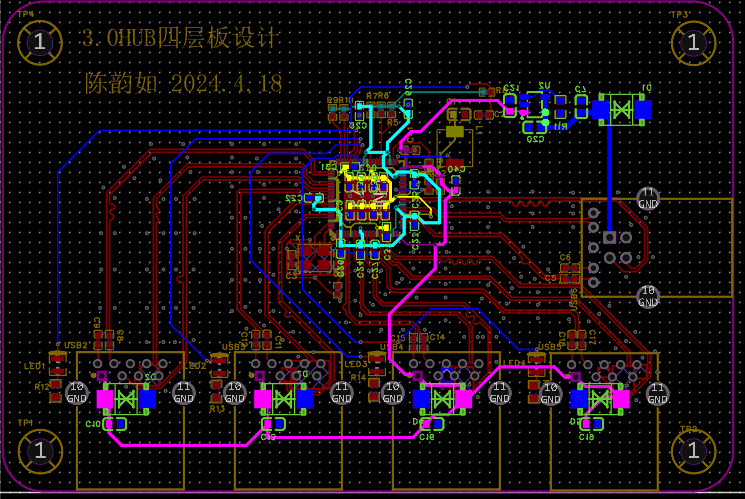

3.0HUB四层板设计

本文最后更新于:2024年4月16日 凌晨

成图校赛学习的四层板PCB设计!

3.0HUB板设计概述

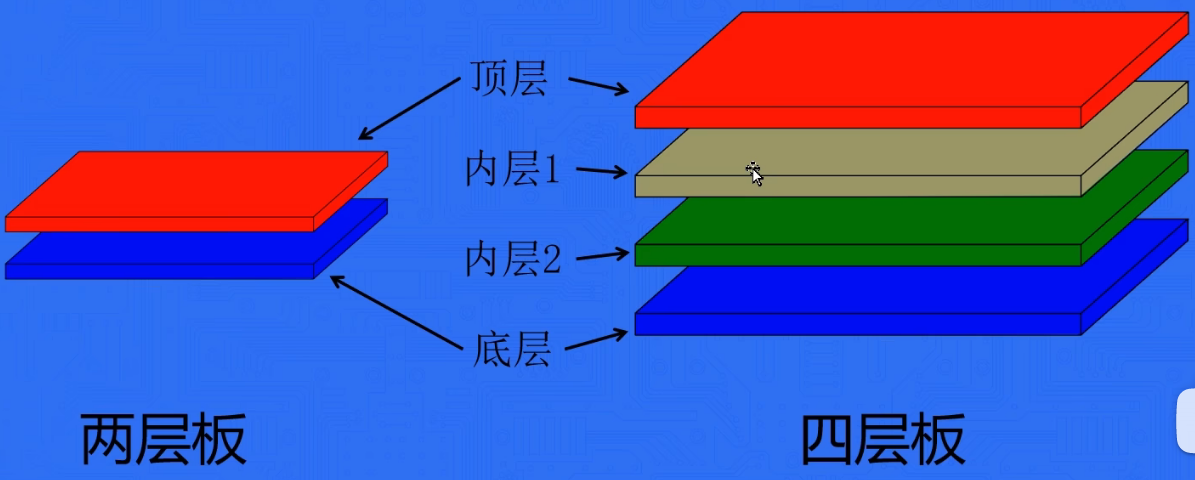

四层板

一般pcb四层板,如下安排:顶层和底层为信号层,中间2层分别为电源层和地层。电源层与地线层在中间可以起到隔离作用,减少干扰的作用。

对于尺寸较大的pcb四层板,元器件比较宽松的PCB板也可以用两层完成,如果两层布局困难,排不开的话,容易造成干扰的,可以使用4层解决过分拥挤的困难。

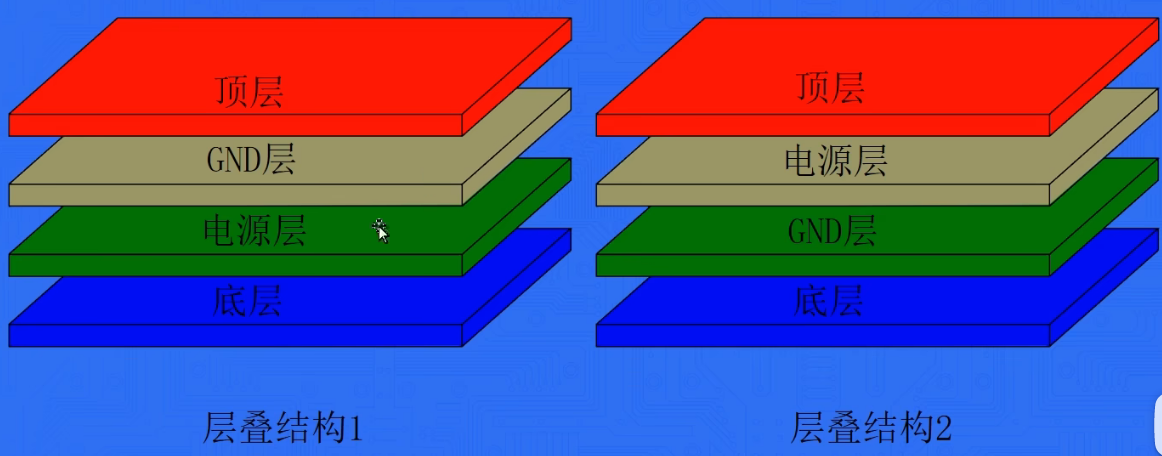

不同的层叠结构有着不同的应用情景,如果器件在顶层布局或者关键信号线在顶层走线连接,GND最好放在第二层,采用层叠结构1;若器件在底层布局或者关键信号线在底层走线连接,则GND最好放在第三层,采用层叠结构2。

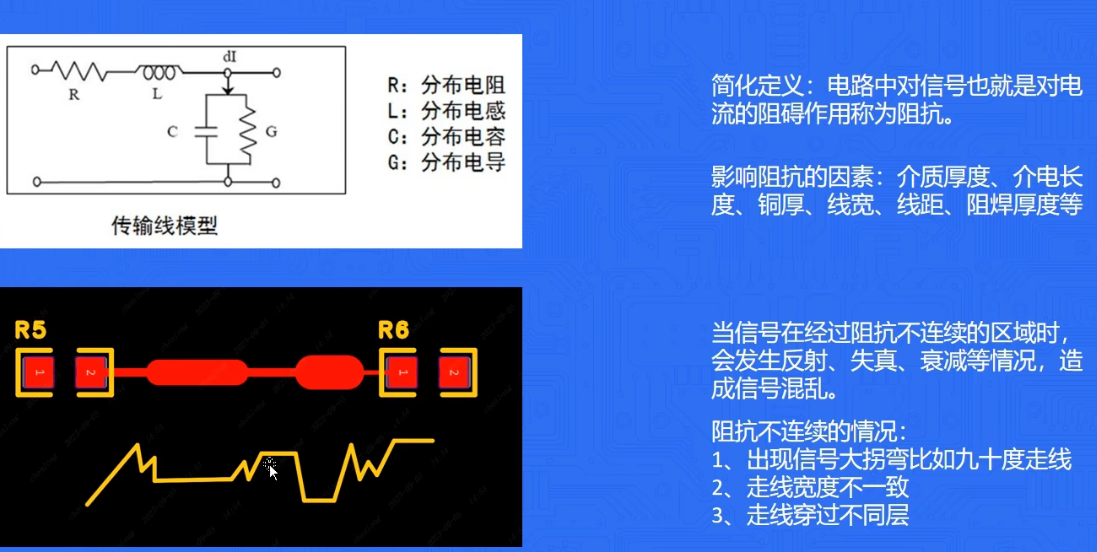

阻抗干扰

嘉立创阻抗计算神器

在嘉立创官网进入阻抗计算服务页面,设置参数,可以一键生成需要的线宽。

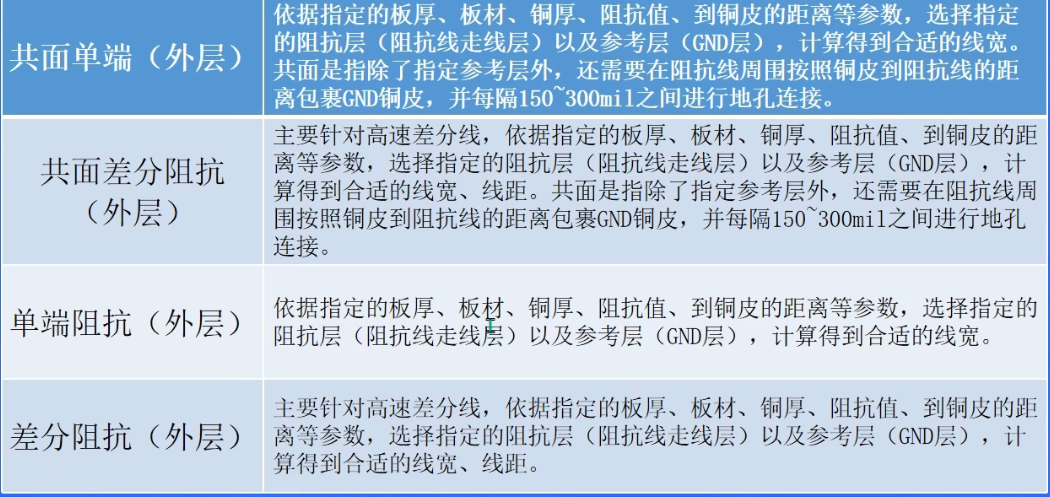

- 四种阻抗模式的选择:

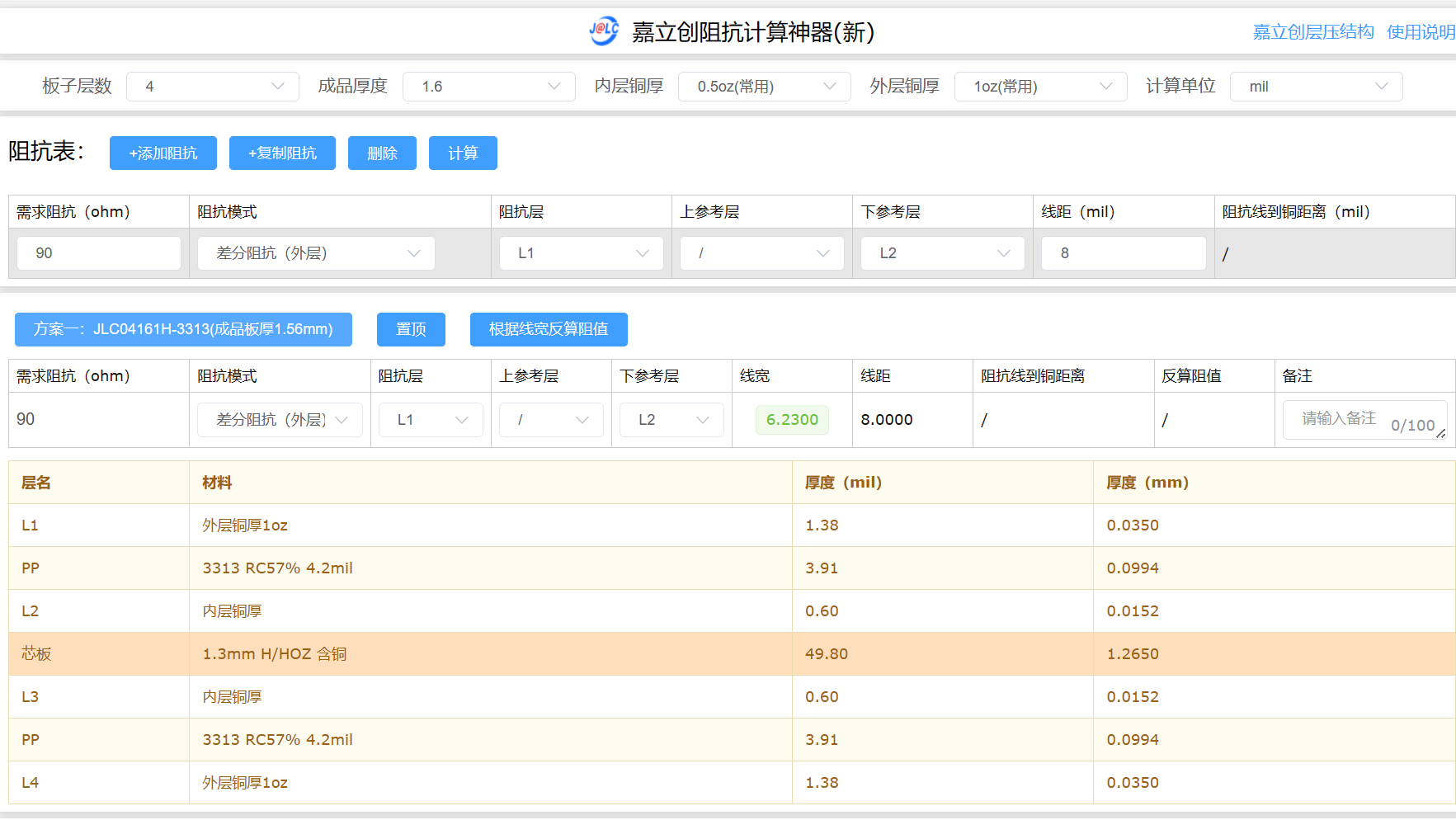

这里假设需求阻抗为90Ω,模式选择差分阻抗,阻抗层为L1,即在顶层进行走线,按照前面的层叠结构1,第二层为GND层,因此下参考层为L2,,间距按照默认8mil。

- 点击计算

- 注意:线宽不能随意设置,需要考虑生产加工的限制,嘉立创多层板的最小线宽为3.5mil,还需要留有一定的余量保证生产合格率,因此嘉立创多层板的最小线宽不要小于6mil。

USB端口设计

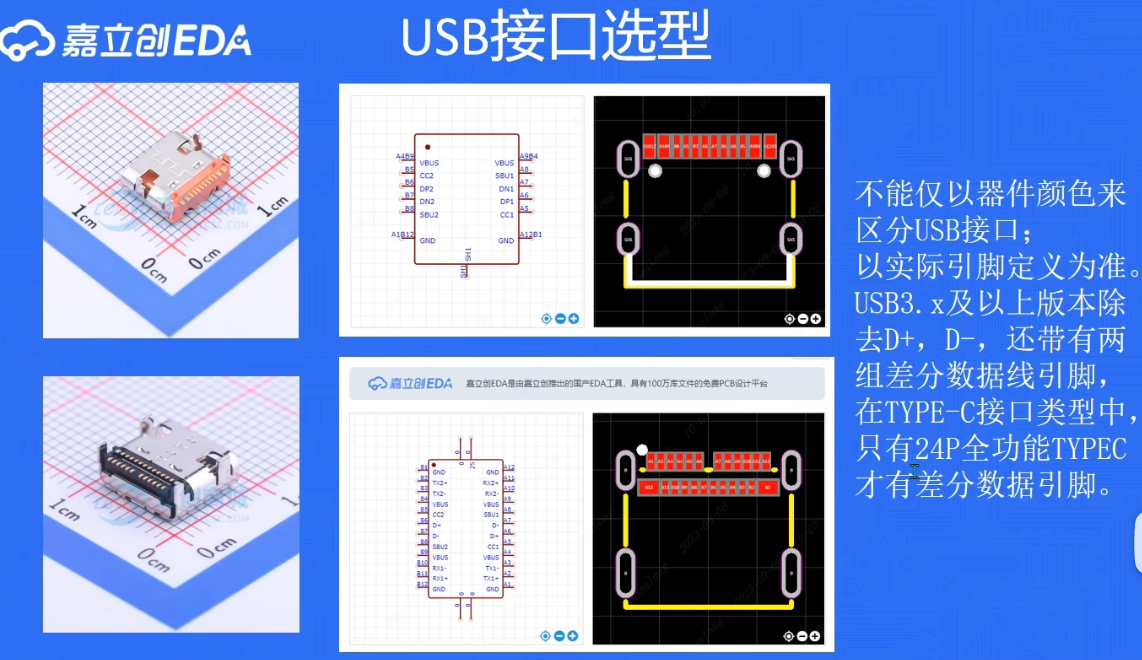

USB接口选型:

- 对于TYPE-C接口类型,只有24P全功能TYPE-C才有差分数据引脚,为USB3.x及以上版本。

- 对于TYPE-B接口类型,外形上就比较好区分。

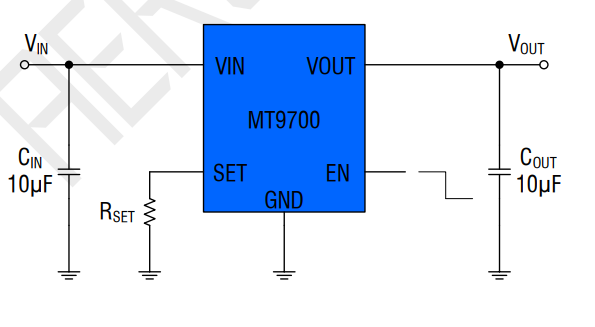

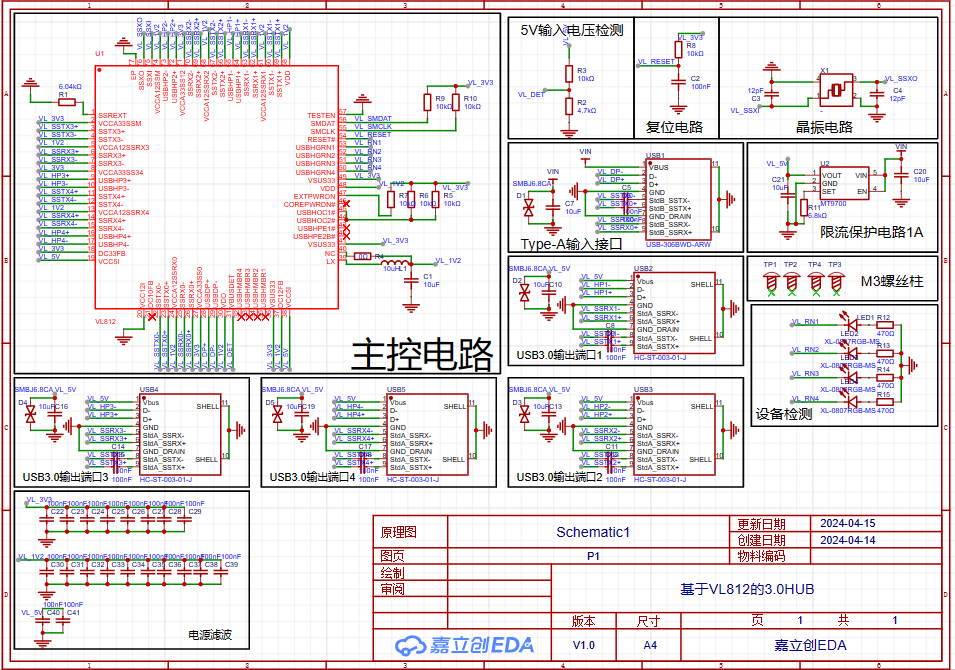

基于VL812的3.0HUB芯片电路设计

新建工程,命名保存之后打开电路图设计界面。

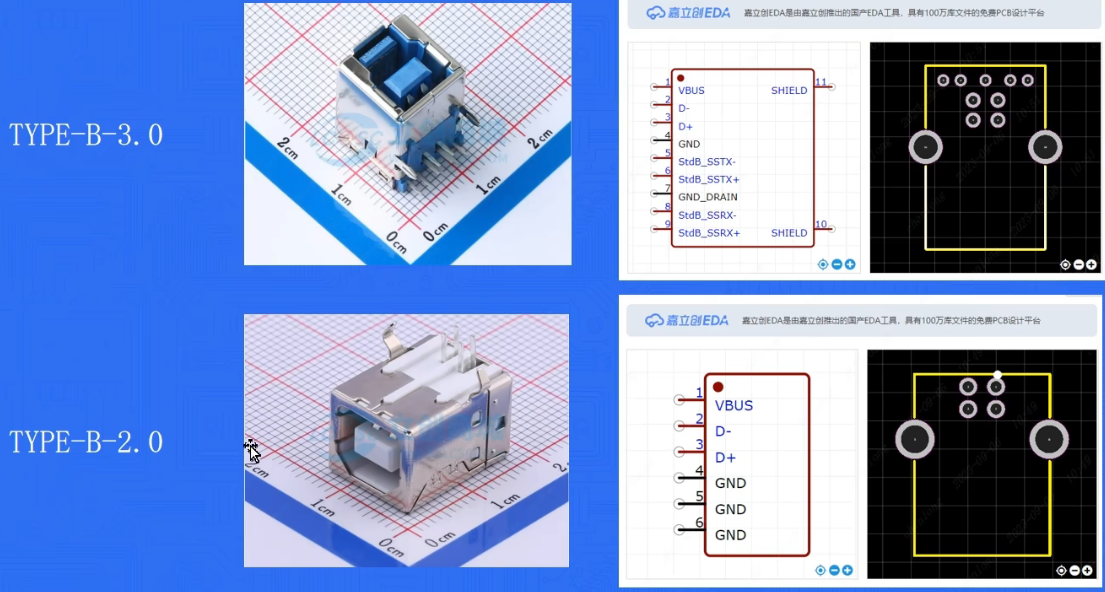

主控芯片VL812

在立创商城搜索VL812芯片,放置,点击属性查看数据手册。

通过Product Features 可以快速了解一款芯片的特性。

点击芯片,右键选择编辑符号,进入符号编辑界面。可以顺带查看每个引脚的功能。

1号引脚SSREXT,官方实例要求连接6.04kΩ的电阻之后再接地。

31号引脚VBUSDET:检测是否存在5V电源的输入,高电平时表示存在高电平输入,低电平表示不存在。

32号-35号引脚都是用来检测过电流的,这里不需要,之间不连接。

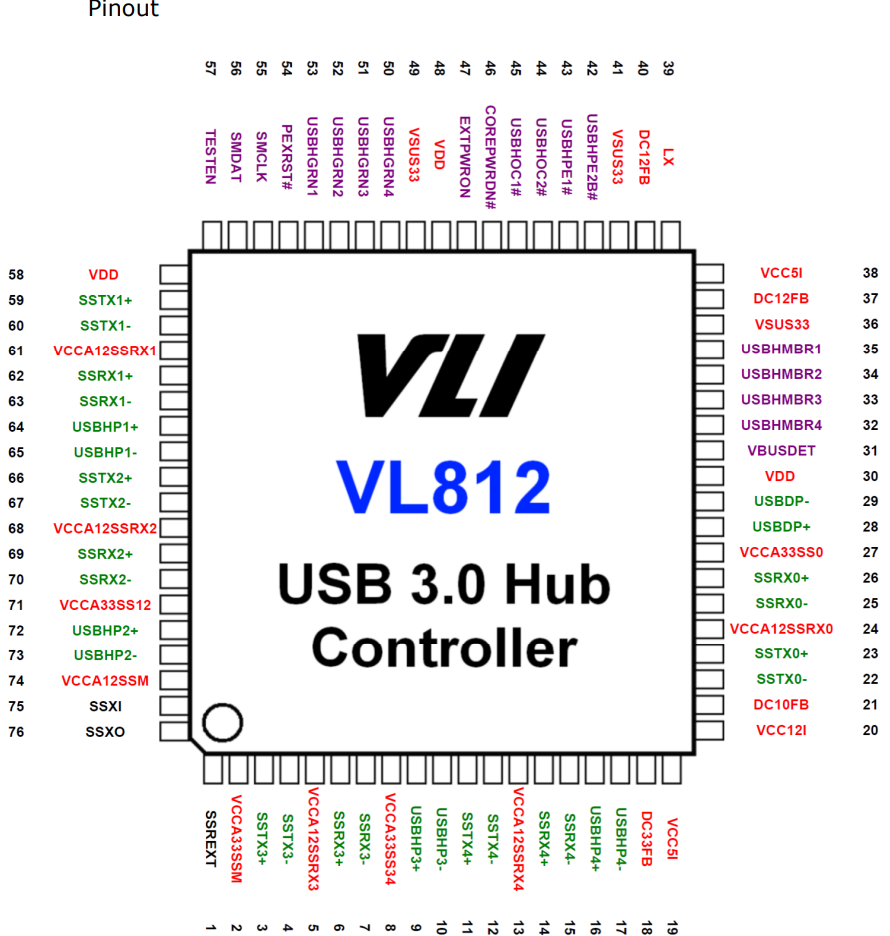

计算晶振匹配电容:

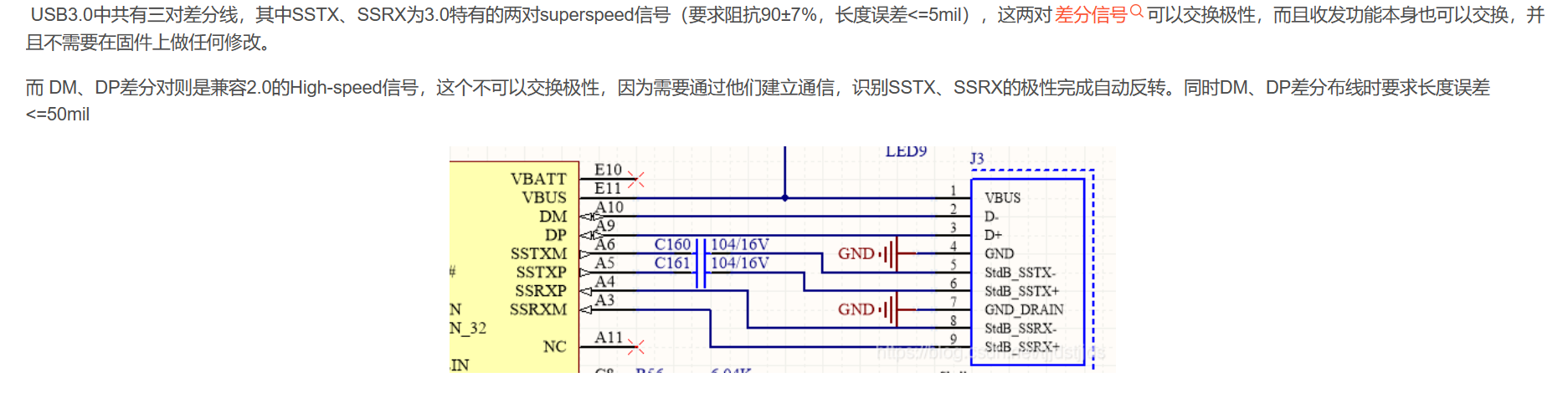

USB3.0差分信号极性问题

小知识:在USB3.0的SSTX信号线中,常常串联一个100NF的贴片电容,减少低频干扰,提升信号质量。

VBUS是USB接口中提供电源电压的信号线。通过VBUS,主机端可以向连接的设备提供所需的电源,使其正常工作。

TVS二极管

TVS即Transient Volatge Suppressor,中文名称:瞬态电压抑制二极管,又称雪崩击穿二极管。在通常情况下,我们称之为TVS二极管。

- 其在电路中的作用主要是保护敏感电路,免受高电压瞬变损坏的组件。其中,大部分用于端口的保护,防止端口瞬间的电压冲击造成后级电路的损坏。其中高压瞬变的主要来源是静电放电,电气快速瞬变和浪涌事件。

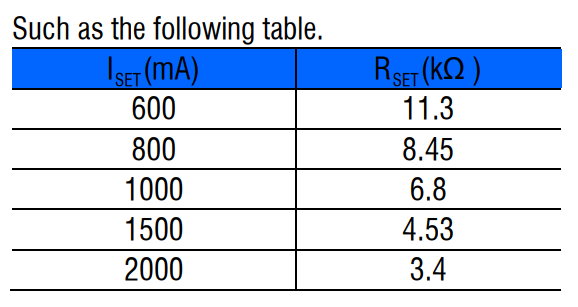

限流保护芯片

这里选用的是MT9700。

螺丝

在常用库中找到螺丝,选择M3,方便后续对板子进行固定

DRC检查

检查原理图的一些问题。

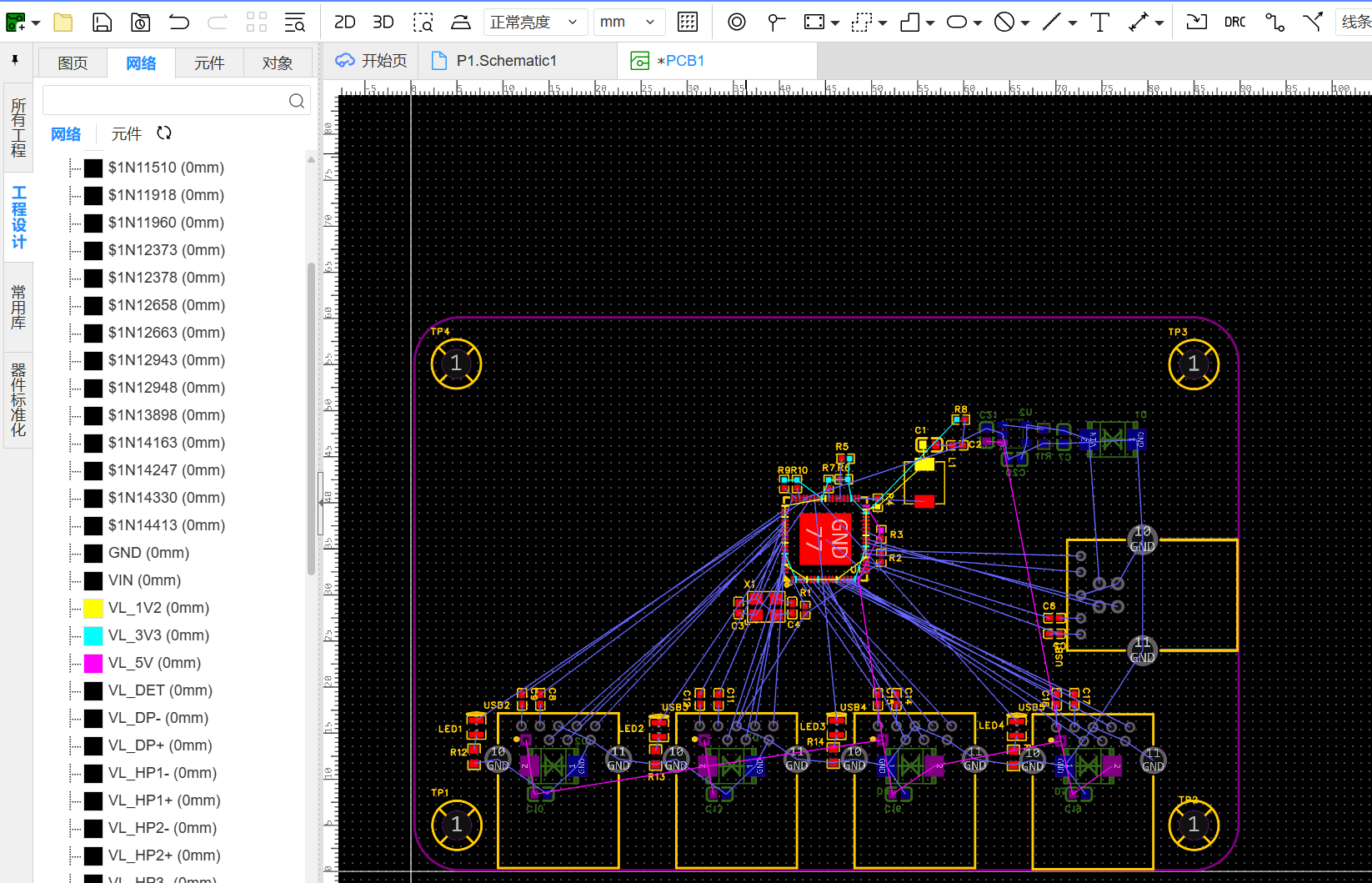

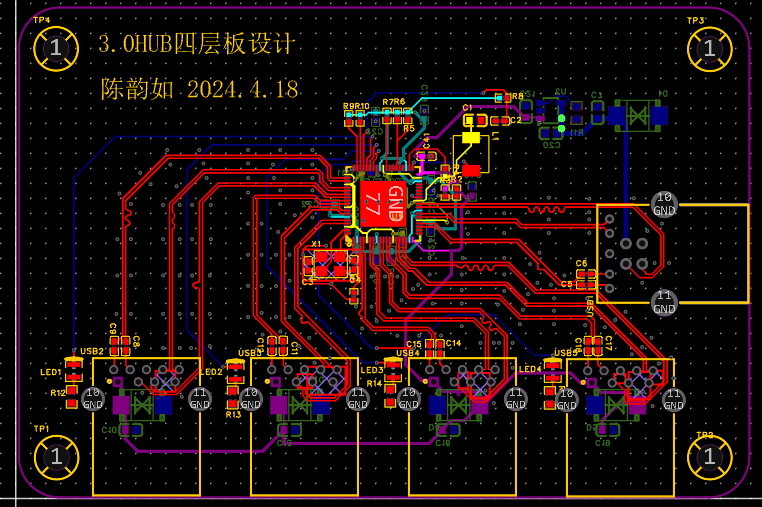

PCB布局

绘制板框范围,倒圆角

嘉立创免费打板的范围是100*100(mm),因此先把这个最大的板框范围画出来。然后点击板框,设置半径为5mm的倒圆角。

粗调元器件的布局

- 调整好之后,固定螺丝的位置,

锁定。 - 四个输出接口,选择底部对齐和水平等距分布,调整好位置之后也点击

锁定。 - 可以点击

工程设计-网络,用不同的颜色区分电源线和信号线,但是注意不要弄成红色、蓝色线(容易跟切换顶层和底层时候的指示色相混淆)。

- 输出电源引脚最好都外接100nF的电容,用于滤波。

- 有多少个

没有外接电容的裸露电源引脚,就放多少个100nF的滤波电容并联。

-顶层是走高速信号线的,因此大量的滤波电容建议放在底面,就近放置,避免造成干扰。

- 有多少个

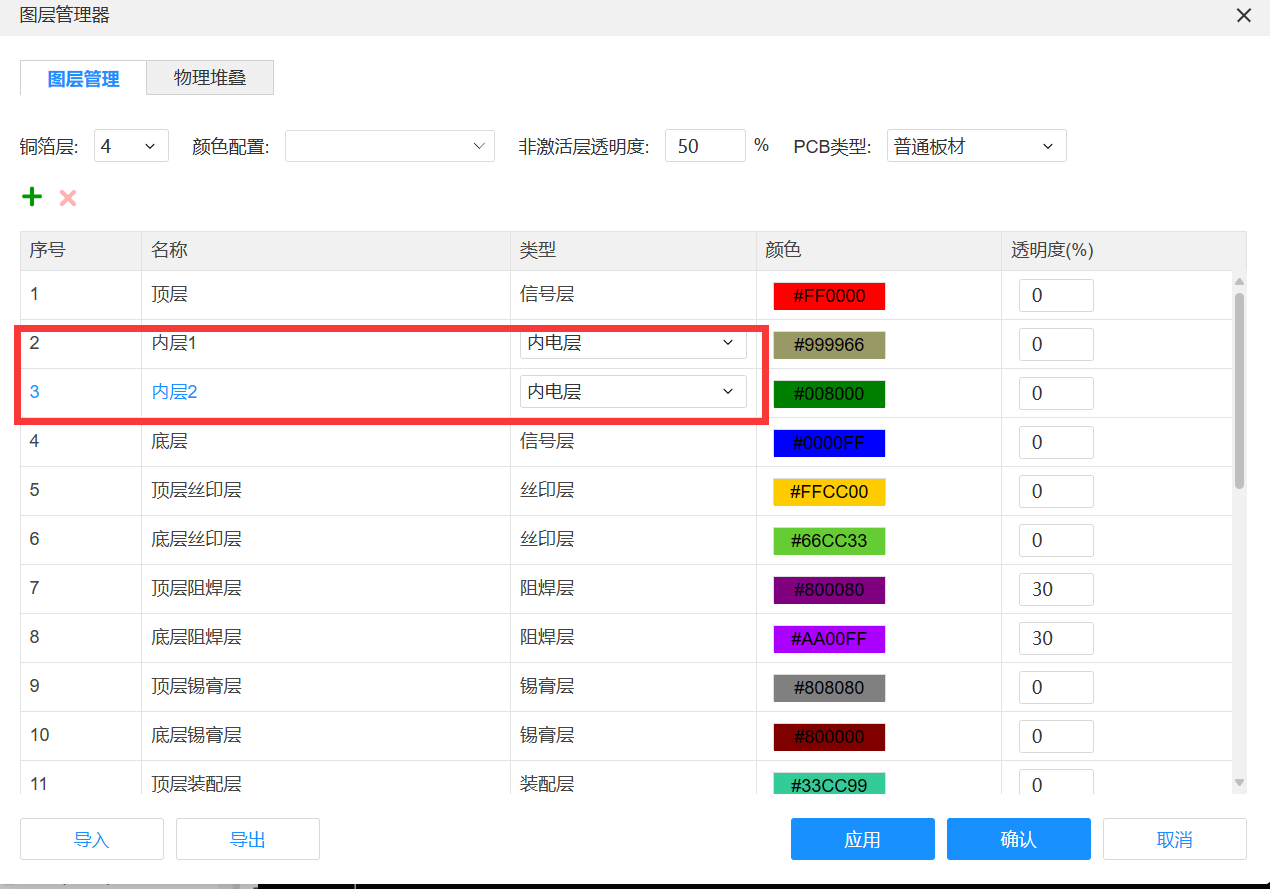

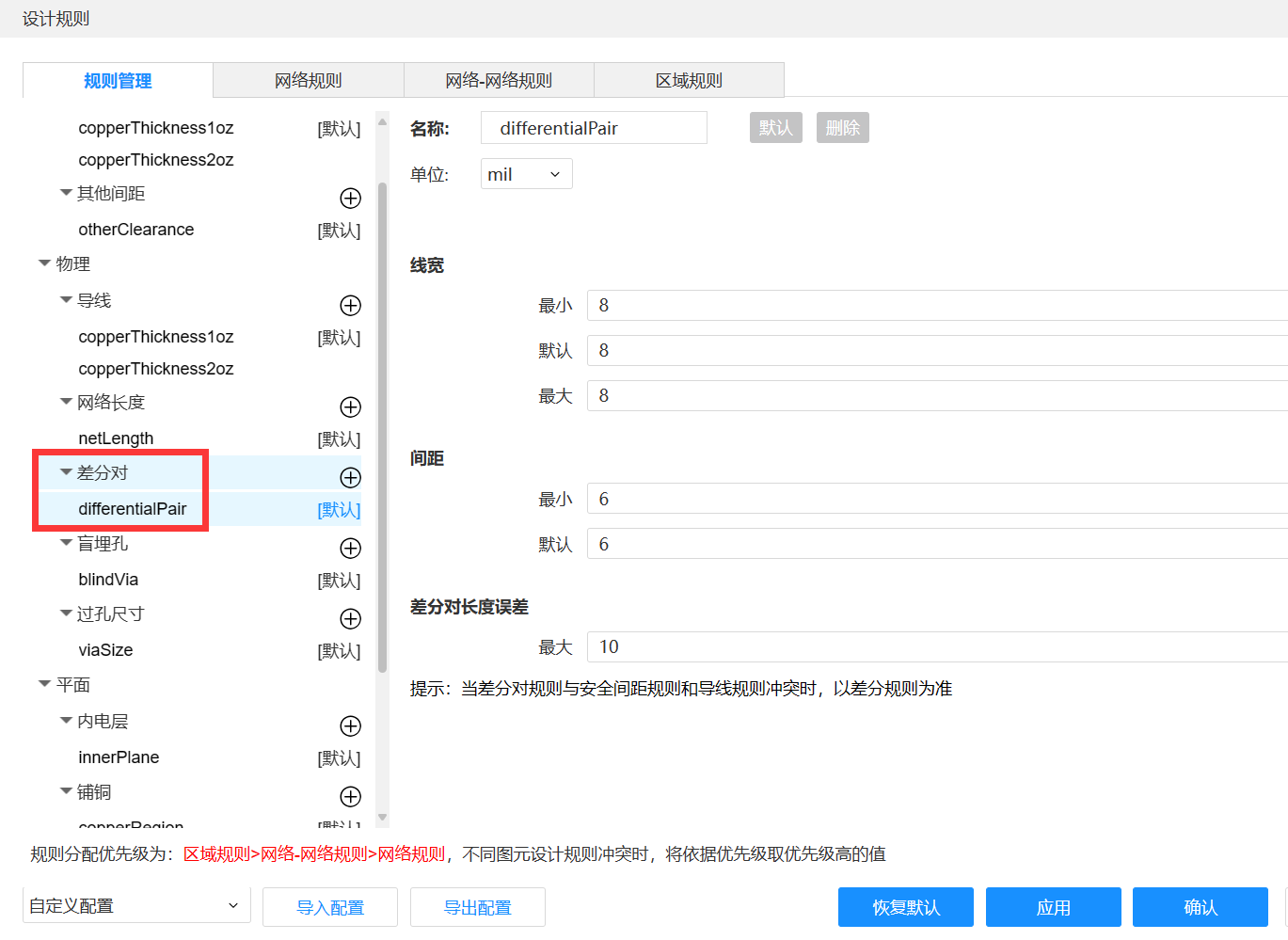

设计规则设置

- 板子层数的设置:点击

工具-图层管理器-铜箔层改为4- 一般将两个内层都设置为内电层,一个用于GND层,一个用于电源层。点击应用,确认保存。

- 内层1和内层2都默认为GND网络。

- 阻抗计算:USB3.0一般需要控制阻抗在90欧姆左右,通过嘉立创的阻抗计算神器计算。

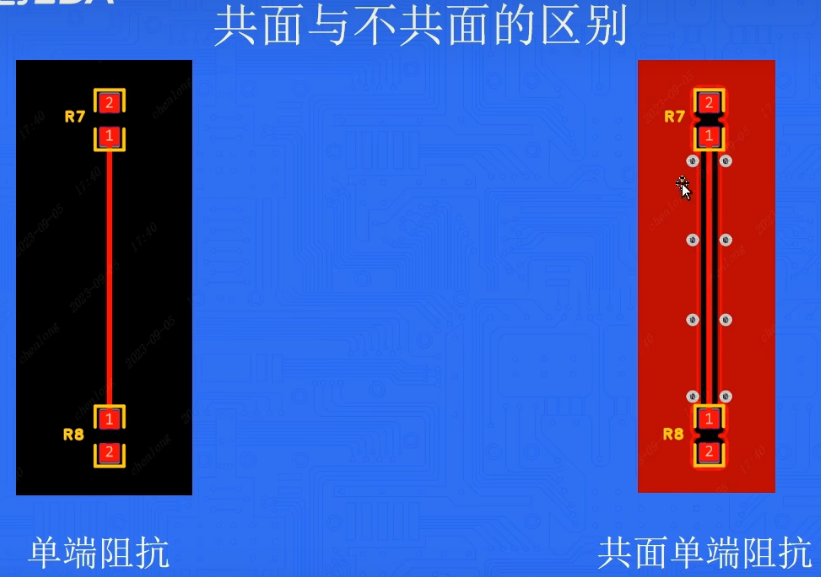

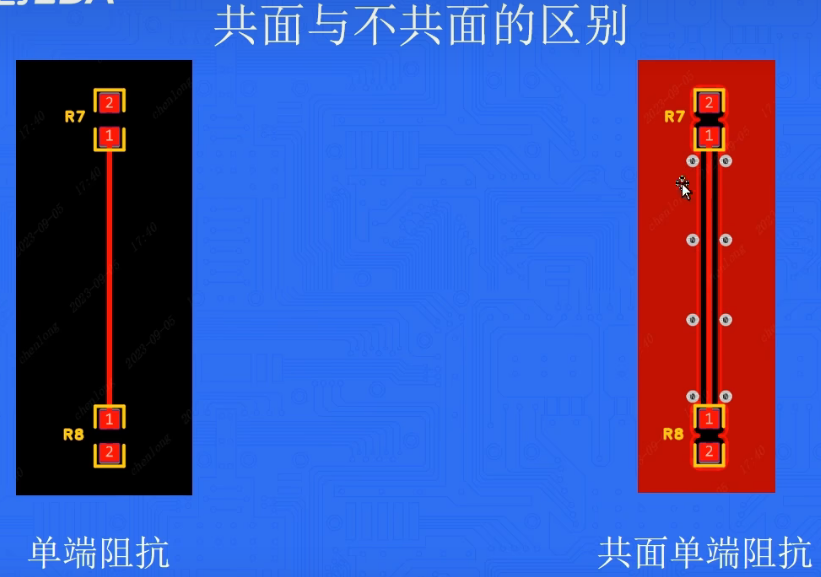

- USB3.0采用的差分信号线,顶层平面元器件不算拥挤,可以使用共面阻抗。因此,选择

共面差分阻抗模式。

-走线层为L1, 即顶层,参考层为GND,为L2,其余参数保持默认。 - 差分线宽为计算得到的数据。

- USB3.0采用的差分信号线,顶层平面元器件不算拥挤,可以使用共面阻抗。因此,选择

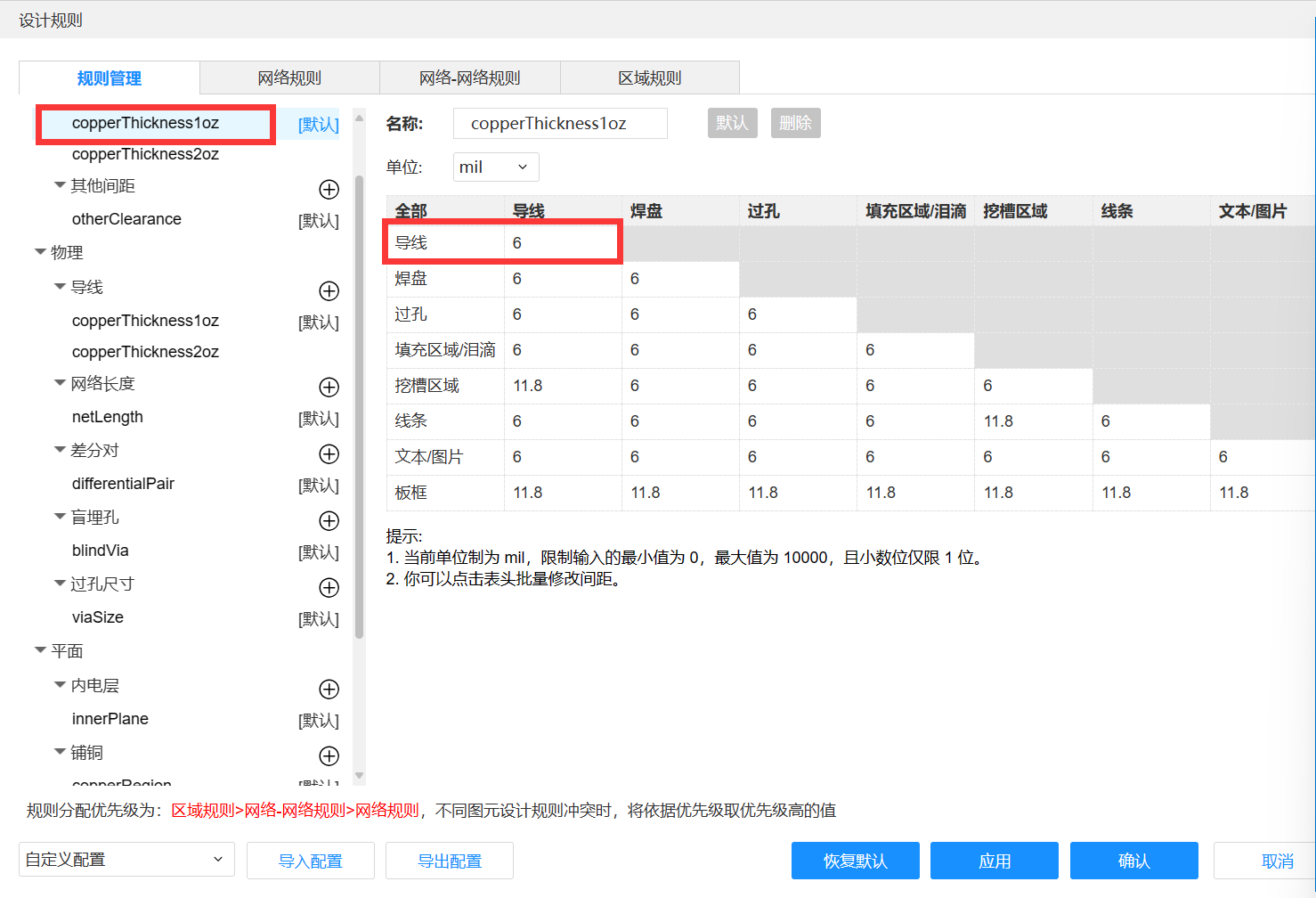

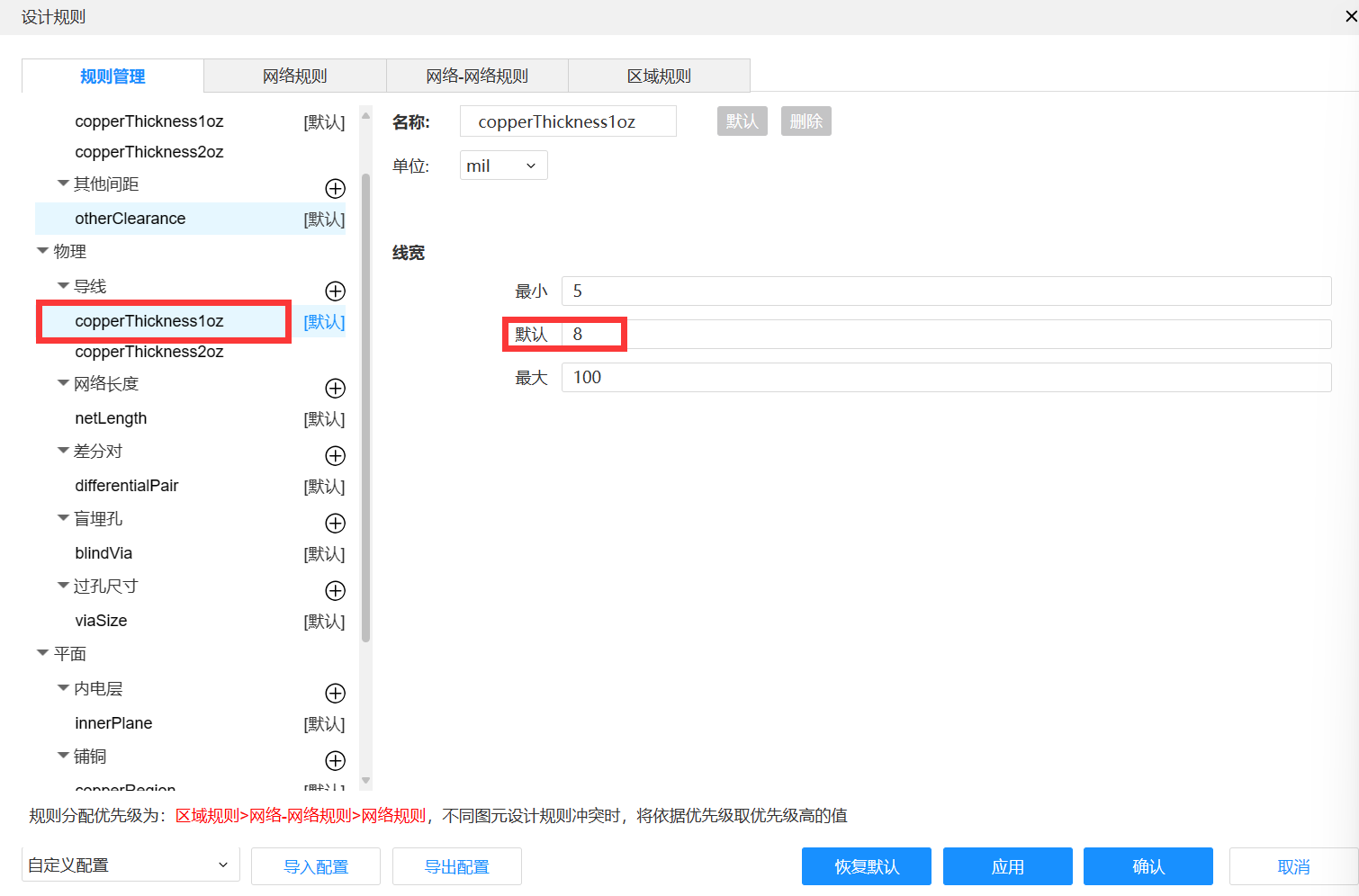

- 回到编辑器页面,选择

设计-设计规则- 安全间距设为6mil,嘉立创的免费打样最低间距不要小于6mil。

-导线线宽设为8mil,默认线宽是10,需要检查默认线宽和芯片的焊盘是否匹配,进行调整。 - 差分线宽严格按照计算数据进行设置。

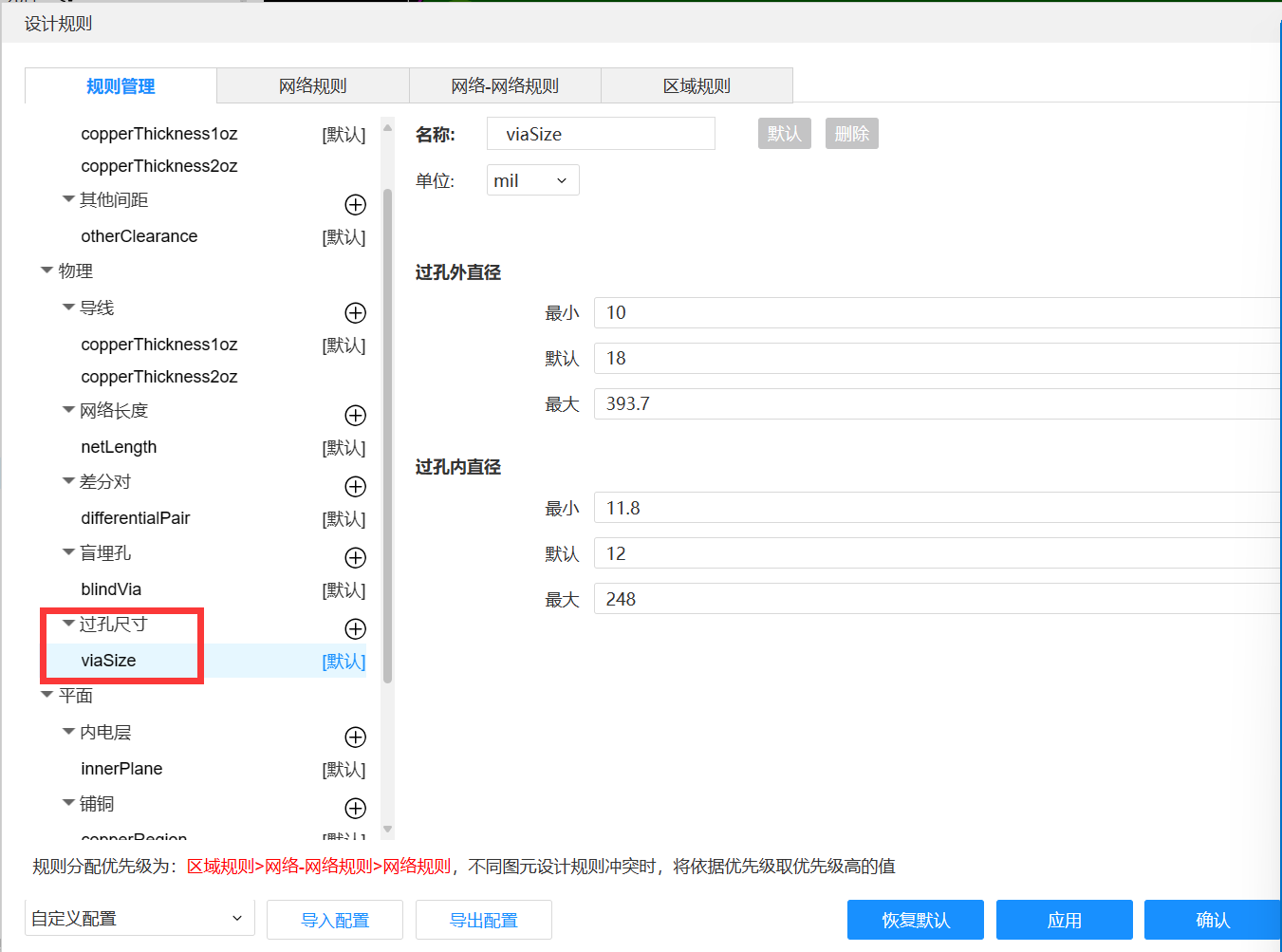

- 过孔尺寸设置:内直径的最小免费尺寸为12mil,不要修改,默认为12即可。外直径进行一定的设置。

-内电层和铺铜:均主要设置到边框/槽孔间距为40mil。

- 安全间距设为6mil,嘉立创的免费打样最低间距不要小于6mil。

走线

先走芯片周围的杂线,再走高速信号线。

- 点击

设计-差分对管理器,设置15组差分对高速信号线。然后选择布线-差分对布线- 布线优先级:优先考虑SSTX和SSRX(USB3.0高速信号线),然后才是HP(USB2.0信号线)。

- 晶振周围需要进行

包地处理。

DRC检查

- 内电层报错:点击内电层,重建内电层。

- 差分线等长调节,单边,一般最小振幅为1mil,最大振幅为24mil(3W原则)。

- GND最后统一铺铜:点击

放置-铺铜-矩形,将整个PCB板框起来,然后顶层和底层铺铜。- 快捷键

shift+m隐藏or展现铺铜。 shift+b重新铺铜。

- 快捷键

- 游离的铜块不利于信号传输,需要进行处理。点击

放置-禁止区域-矩形 - 有些时候3D视角的元器件不显示,应该是嘉立创没有更新元件的3D视图,换一个商家的试试应该就可以。

最终成品展示

- 原理图:

- PCB板子:

- 3D模型: